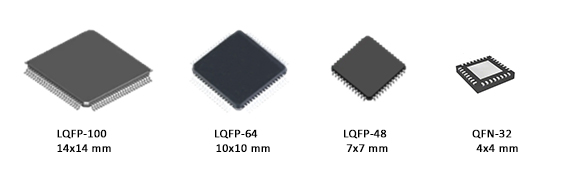

AGRV2K CPLDs is the lowest cost CPLDs. This instant-on, non-volatile CPLD family targets general-purpose and low-density logic. The logic density is 2K Logic Elements with LQFP-100(AGRV2KL100) , LQFP-64(AGRV2KL64) , LQFP-48(AGRV2KL48) and QFN-32 (AGRV2KQ32) packages.

- Lowest Cost and low-power CPLD

- Instant-on, non-volatile standard compatible architecture.

- Up to 4 global clock lines in the global clock network that drive throughout the entire device.

- Provides programmable fast propagation delay and clock-to-output times.

- Provides PLL per device, clock multiplication, and phase shifting.

- Contains 4 Embedded Block RAMs (EBRs) M9K, that can be configured to provide various memory functions, such as RAM, shift registers, ROM, and FIFO.

- Supports 3.3-V logic level

- Programmable slew rate, drive strength, bus-hold, programmable pull-up resistors, open-drain output, Schmitt triggers and programmable input delay.

- Built-in Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry complaint with IEEE Std. 1149.1-1990

- ISP circuitry compliant with IEEE Std. 1532

- On-Chip oscillator is provided to support frequency to 8 MHz

- 3.3-V LVCMOS and LVTTL standards

Download datasheet