buy naltrexone canada

buy

low dose naltrexone canada

buy naltrexone canada

buy

low dose naltrexone online

melatonin and weed before bed

melatonin and weed safe

link

where can i get an abortion pill near me

where can i get an abortion pill online

go

sertraline 50mg

sertraline 50mg tablets

click

acquistare cialis originale

generico cialis

italia

bentelan tosse

bentelan e tachipirina

open

viagra prodej praha

viagra cena apoteka

open

lexapro pregnancy risk category

lexapro and

pregnancy

cheap abortions

abortion

at 10 weeks

cetirizin actavis 10 mg

cetirizin uden

recept

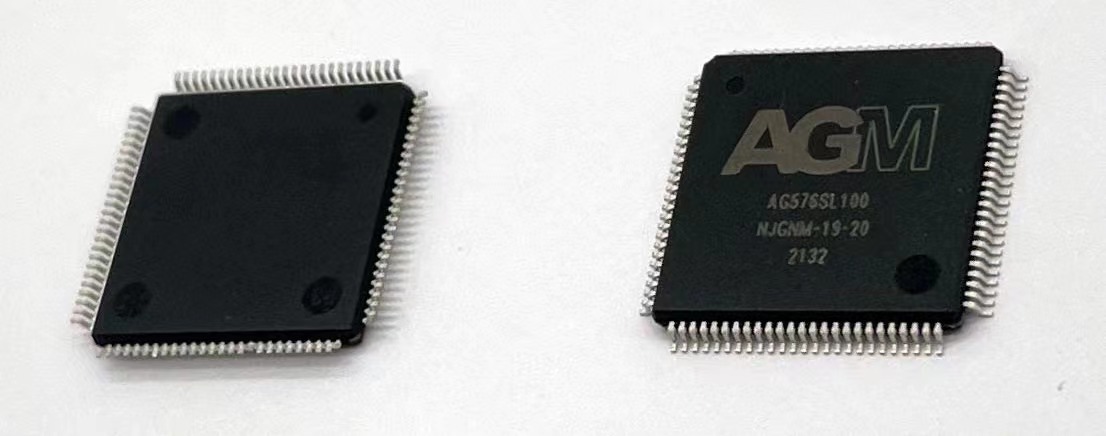

AG576 CPLDs is the low cost CPLDs. This instant-on, non-volatile CPLD family targets general-purpose and low-density logic. The logic density is 576 Logic Elements with LQFP-100 and 144 package.

- Low-Cost and low-power CPLD

- Instant-on, non-volatile standard compatible architecture.

- Up to 4 global clock lines in the global clock network that drive throughout the entire device.

- Provides programmable fast propagation delay and clock-to-output times.

- Provides PLL per device, clock multiplication, and phase shifting.

- UFM supports non-volatile storage up to 256 Kbits.

- Supports 3.3-V logic level

- Programmable slew rate, drive strength, bus-hold, programmable pull-up resistors, open-drain output, Schmitt triggers and programmable input delay.

- Built-in Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry complaint with IEEE Std. 1149.1-1990

- ISP circuitry compliant with IEEE Std. 1532

- 3.3-V LVCMOS and LVTTL standards

- Emulated LVDS output (LVDS_E_3R)

- Emulated RSDS output (RSDS_E_3R)

Download datasheet

EVB schematics